## Description

The μPD7261A and μPD7261B hard-disk controllers are intelligent microprocessor peripherals designed to control a number of different types of disk drives. They are capable of supporting either hard-sector or soft-sector disks and provide all control signals that interface the controller with either SMD disk interfaces or ST506-type drives. The sophisticated instruction set minimizes the software overhead for the host microprocessor. By using the DMA controller, the microprocessor needs only to load a few command bytes into the µPD7261A/7261B and all the data transfers associated with read, write, or format operations are done by the µPD7261A/7261B and the DMA controller. Extensive error reporting, verify commands, ECC, and CRC data error checking assure reliable controller operation. The µPD7261A/7261B provides internal address mark detection, ID verification, and CRC or ECC checking and verification. An eightbyte FIFO is used for loading command parameters and obtaining command results. This makes the structuring of software drivers a simple task. The FIFO is also used for buffering data during DMA read/write operations.

#### **Features**

- ☐ Flexible interface to various types of hard disk drives

☐ Programmable track format

☐ Control on the State of the state

- Controls up to 8 drives in SMD mode; up to 4 drives in ST506-type mode

- ☐ Parallel seek operation capability

- ☐ Multi-sector and multi-track transfer capability

- Data scan and data verify capability

- High-level commands, including:

Read Data, Read ID, Write Data, Format, Scan Data, Verify Data, Verify ID, Check, Seek (normal or buffered), Recalibrate (normal or buffered), Read Diagnostic (SMD only), Specify, Sense Interrupt Status, Sense Unit Status, and Detect Error

- □ NRZ or MFM data format

- ☐ Maximum R/W CLK frequency:

- 12 MHz (7261A)

- -- 18 MHz (7261B-18)

- 23 MHz (7261B-23)

- ☐ Error detection and correction capability

- ☐ Simple I/O structure: compatible with most microprocessors

- ☐ All inputs and outputs except clock pins are TTL-compatible (clock pins require pullup)

- ☐ Data transfers under DMA control

- □ NMOS

- ☐ Single +5-volt power supply

- ☐ 40-pin ceramic DIP

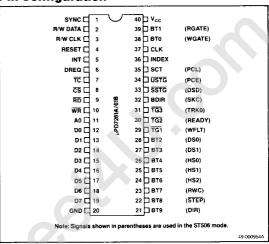

## **Pin Configuration**

# **Ordering Information**

| Device Number | nber Package Type  |                |  |  |

|---------------|--------------------|----------------|--|--|

| μPD7261AD     | 40-pin ceramic DIP | 12 MHz         |  |  |

| μPD7261BD-18  | 40-pin ceramic DIP | 18 <b>M</b> Hz |  |  |

| μPD7261BD-23  | 40-pin ceramic DIP | 23 MHz         |  |  |

#### Pin Identification

| Liu idelinik   | cation                         |                            |

|----------------|--------------------------------|----------------------------|

| No.            | Symbol                         | Function                   |

| Host interface |                                |                            |

| 4              | RESET                          | Reset input                |

| 5              | INT                            | Interrupt request output   |

| 6              | DREQ                           | DMA request output         |

| 7              | ŤĈ                             | Terminal count input       |

| 8              | CS                             | Chip select input          |

| 9              | RD                             | Read strobe input          |

| 10             | WR                             | Write strobe input         |

| 11             | A <sub>0</sub>                 | Register select input      |

| 12-19          | D <sub>0</sub> -D <sub>7</sub> | Data I / 0 bus             |

| 20             | GND                            | Ground                     |

| 37             | CLOCK                          | External clock input       |

| 40             | Vcc                            | +5 V power supply          |

| SMD Interface  |                                |                            |

| 1 0            | ◆ SYNC                         | PLL synchronization output |

| 2              | R / W DATA                     | Read / write data I / 0    |

| 3              | R/W CLK                        | Read / write clock input   |

|                |                                |                            |

Pin Identification (cont)

| No.                  | Symbol     | Function                            |

|----------------------|------------|-------------------------------------|

| SMD Interface (cont) |            |                                     |

| 21–28, 38, 39        | BT9-BT0    | Bit 9–0 outputs / Status inputs     |

| 29-31                | TG1-TG3    | Tag 1–3 output                      |

| 32                   | BDIR       | Bit direction output                |

| 33                   | SSTG       | SR select tag output                |

| 34                   | ÜSTG       | Unit select tag output              |

| 35                   | SCT        | Sector input                        |

| 36                   | INDEX      | Sector zero input                   |

| ST506-Type Interface |            |                                     |

| 1                    | SYNC       | PLL lock / Read clock enable output |

| 2                    | R / W DATA | Read / write data   / 0             |

| 3                    | R/W CLK    | Read / write clock input            |

| 21                   | DIR        | Direction in output                 |

| 22                   | STEP       | Step pulse output                   |

| 23                   | RWC        | Reduced write current<br>output     |

| 24-26                | HS2-HS0    | Head select outputs 2-0             |

| 27, 28               | DS1, DS0   | Drive select outputs 1, 0           |

| 29                   | WFLT       | Write fault input                   |

| 30                   | READY      | Ready input                         |

| 31                   | TRK0       | Track zero input                    |

| 32                   | SKC        | Seek complete input                 |

| 33                   | DSD        | Drive selected input                |

| 34                   | PCE        | Precomp early output                |

| 35                   | PCL        | Precomp late output                 |

| 36                   | INDEX      | Index input                         |

| 38                   | WGATE      | Write gate output                   |

| 39                   | RGATE      | Read gate output                    |

#### Pin Functions — Host Interface

#### **RESET (Reset)**

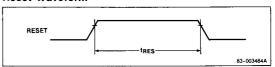

When the RESET input is pulled high, it forces the device into an idle state. The device remains idle until a command is issued to the system.

#### INT (Interrupt Request)

The  $\mu$ PD7261A/7261B pulls the INT output high to request an interrupt.

## **DREQ (DMA Request)**

The  $\mu$ PD7261A/7261B pulls the DREQ output high to request a DMA transfer between the disk controller and the memory.

## TC (Terminal Count)

The TC input goes low to signal the final DMA transfer.

# CS (Chip Select)

When the  $\overline{CS}$  input is low, it enables reading from or writing to the register selected by  $A_0$ .

## RD (Read Strobe)

When the  $\overline{\text{RD}}$  strobe is low, data is read from the selected register.

## WR (Write Strobe)

When the  $\overline{WR}$  input is low, data is written to the selected register.

## A<sub>0</sub> (Register Select)

The  $A_0$  input is connected to a non-multiplexed address bus line. When  $A_0$  is high, it selects the command or status register. When it is low, it selects the data buffer.

## D<sub>0</sub>-D<sub>7</sub> (Data Bus)

D<sub>0</sub>-D<sub>7</sub> are connected to the system data bus.

### **CLOCK (Clock)**

The CLOCK input is the timing clock for the on-chip processor.

#### Pin Functions — SMD Interface

# **SYNC (PLL Synchronization)**

This output goes high after the read gate signal (BT1 when  $\overline{TG3} = 0$ ) is high and a given number of bytes (GPL2-2) has elapsed.

#### R/W DATA (Read/Write Data)

The R/W DATA pin outputs the write data to the drive, and inputs the read data from the drive.

## R/W CLK (Read/Write Clock)

R/W CLK is the input for the read and write clocks.

#### BT9-BT0 (Bit 9-0)

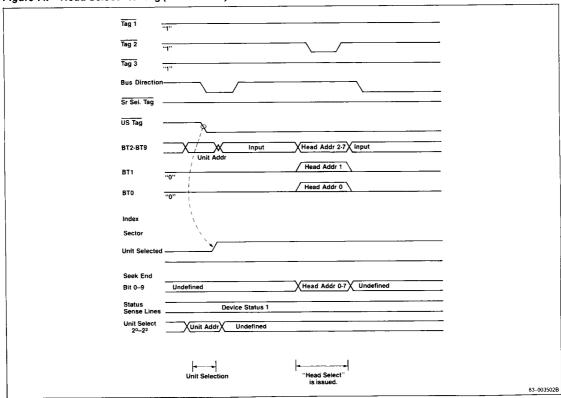

BT9-BT0 output the bit signals, bit 9-0. The bit 9-0 outputs send cylinder and unit addresses to the drives. BT9-BT2 also act as inputs for status signals from the drives as shown in table 1.

Table 1. Bit and Control Information

| No. | Bit | Control         |

|-----|-----|-----------------|

| 21  | ВТ9 | Unit Selected   |

| 22  | BT8 | Seek End        |

| 23  | BT7 | Write Protected |

| 24  | BT6 |                 |

| 25  | BT5 | Unit Ready      |

| 26  | BT4 | On Cylinder     |

| 27  | BT3 | Seek Error      |

| 28  | BT2 | Fault           |

BT7-BT2 also read the device status 2 (SR7-SR2) and device type (DT7-DT2). The index and SCT pins read SR0, SR1 and DT0, DT1.

### **BDIR (Bit Direction)**

The BDIR output determines whether pins 28-21 will output BT2-BT9 or input drive status signals.

# TG3-TG1 (Tag 3-1)

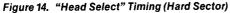

The  $\overline{TG}$  outputs define the use of the BT pins. When  $\overline{TG1}$  is low, BT9-BT0 output the cylinder address. When  $\overline{TG2}$  is low, BT7-BT0 select a head address. When  $\overline{TG3}$  is low, BT9-BT0 output control signals for the disk drive.

## SSTG (SR Select Tag)

When the SSTG output is low, BT7-BT2, INDEX and SCT will be inputting SR7-SR0 or DT7-DT0.

# **USTG (Unit Select Tag)**

When the USTG output is low, BT4-BT2 will be outputting a unit address.

### INDEX (Index)

The INDEX input goes high when the drive detects an index mark. INDEX also acts as the SR0 and DT0 input pin.

#### SCT (Sector)

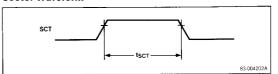

The SCT input goes high when the drive detects a sector mark. SCT also acts as the SR1 and DT1 input pin.

# Pin Functions — ST 506-Type Interface

# SYNC (Read Clock Enable)

SYNC indicates that a sync pattern has been detected and that synchronization has been achieved.

#### R/W DATA (Read/Write Data)

The R/W DATA pin outputs the write data to the drive, and inputs the read data from the drive.

## R/W CLK (Read/Write Clock)

R/W CLK is the input for the read and write clocks.

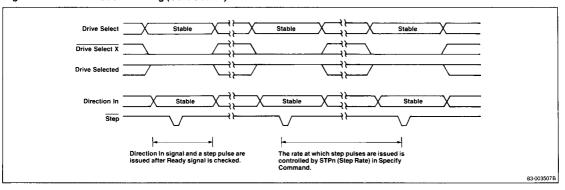

# DIR (Direction In)

The DIR output determines the direction the read/write head will move in when it receives a step pulse. DIR high will cause the head to move inward, DIR low will move the head outward.

## STEP (Step Pulse)

STEP outputs the head step pulses.

## **RWC (Reduced Write Current)**

The RWC output signals that the read/write head of the disk drive has selected a cylinder address larger than that specified in the SPECIFY command. This signal is used to reduce the write current.

### HS2-HS0 (Head Select 2-0)

The HS2-HS0 outputs select the head. Up to 8 read/write heads can be selected per drive.

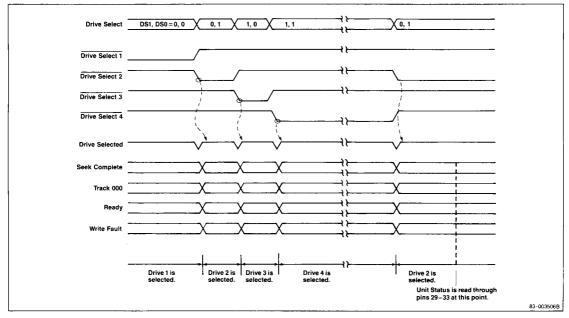

#### DS1, DS0 (Drive Select 1,0)

The DS1 and DS0 outputs select one of up to 4 drives.

### WFLT (Write Fault)

The WFLT input detects write faults.

#### READY (Ready)

The READY input detects the drive's ready state.

#### TRK0 (Track 0)

The TRK0 input signals that the head is at track 0.

#### SKC (Seek Complete)

The SKC input signals that a seek is complete.

#### DSD (Drive Selected)

The DSD input signals that the drive is selected.

## PCE (Precomp Early)

When the PCE output is high, early write precompensation is required.

#### PCL (Precomp Late)

When the PCL output is high, late write precompensation is required.

#### INDEX (Index)

The INDEX input goes high when the drive detects the index mark.

## **WGATE (Write Gate)**

WGATE output goes high when the  $\mu PD7261A/7261B$  is writing data.

## **RGATE (Read Gate)**

The RGATE output goes high when the  $\mu$ PD7261A/7261B is reading from the disk.

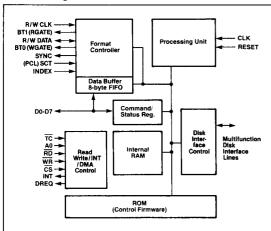

# **Block Diagram**

# **Absolute Maximum Ratings**

| •                                                          |                 |

|------------------------------------------------------------|-----------------|

| Operating temperature, T <sub>OPT</sub>                    | 0°C to +70°C    |

| Storage temperature, T <sub>STG</sub>                      | -65°C to +150°C |

| Voltage on any pin with respect to ground, V <sub>CC</sub> | -0.5 to +7.0 V* |

| Input voltage, V <sub>I</sub>                              | -0.5 to +7.0 V* |

| Output voltage, V <sub>0</sub>                             | -0.5 to +7.0 V* |

Comment: Exposing the device to stresses above those listed in the Absolute Maximum Ratings could cause permanent damage. The device should not be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Characteristics**

\* $\mu$ PD7261B specifications are preliminary  $T_A = 0$  to +70°C,  $V_{CC} = +5.0$  V  $\pm$  10% unless otherwise specified

|                           |                  |      | Limite | 3                   |      | Test                                                                        |

|---------------------------|------------------|------|--------|---------------------|------|-----------------------------------------------------------------------------|

| Parameter                 | Symbol           | Min  | Тур    | Max                 | Unit | Conditions                                                                  |

| Input voltage<br>low      | V <sub>IL1</sub> | -0.5 |        | +0.8                | ٧    | All except CLK,<br>R/WCLK                                                   |

| Input voltage<br>low      | V <sub>IL2</sub> | -0.5 |        | +0.6                | ٧    | CLK, R/WCLK                                                                 |

| Input voltage<br>high     | V <sub>IH1</sub> | +2.0 |        | V <sub>CC</sub> +0. | 5 V  | All except CLK,<br>R/WCLK                                                   |

| Input voltage<br>high     | V <sub>IH2</sub> | +3.3 |        | V <sub>CC</sub> +0. | 5 V  | CLK, R/WCLK                                                                 |

| Output voltage low        | V <sub>OL</sub>  |      |        | +0.45               | ٧    | $l_{OL} = +2.0  \text{mA}$                                                  |

| Qutput voltage<br>high    | V <sub>OH1</sub> | +2.4 |        |                     | ٧    | $l_{OH} = -100 \mu\text{A}$ ,<br>all except pins<br>21–34                   |

| Output voltage<br>high    | V <sub>OH2</sub> | +2.4 |        |                     | ٧    | $I_{OH} = -50 \mu\text{A},$<br>pins 21–34                                   |

| Input leakage<br>current  | l <sub>LI1</sub> |      |        | ± 10                | μÄ   | V <sub>IN</sub> = V <sub>CC</sub> to<br>0.45 V,<br>all except pins<br>21–34 |

| Input leakage<br>current  | I <sub>LI2</sub> |      | •      | -500<br>(7261A)     | μА   | V <sub>IN</sub> = V <sub>CC</sub> to<br>0.45 V;                             |

|                           |                  |      |        | - 700<br>(7261B)    | μΑ   | pins 21–34                                                                  |

| Output leakage<br>current | ILO              |      |        | ±10                 | μА   | V <sub>OUT</sub> = V <sub>CC</sub> to 0.45 V                                |

| Supply current            | lcc              |      | 250    | 320                 | mA   |                                                                             |

## Capacitance

$T_A = 25$  °C,  $V_{CC} = 0$  V

|                            |                  |     | Limits |     |      | Test<br>Conditions |  |

|----------------------------|------------------|-----|--------|-----|------|--------------------|--|

| Parameter                  | Symbol           | Min | Тур    | Max | Unit |                    |  |

| Input<br>capacitance       | C <sub>IN</sub>  |     | ·      | 15  | рF   | (Note 1)           |  |

| Output<br>capacitance      | C <sub>OUT</sub> |     |        | 15  | pF   | (Note 1)           |  |

| Input / Output capacitance | C <sub>1/0</sub> |     |        | 20  | pF   | (Note 1)           |  |

#### Note:

(1) f = 1 MHz, All unmeasured pins tied to GND.

<sup>\*</sup>T<sub>A</sub> = 25°C

**AC Characteristics**

$T_A = 0 \text{ to } +70 \,^{\circ}\text{C}; V_{CC} = +5 \,^{\circ}\text{V} \pm 10 \,^{\circ}\text{C}; C_L = 100 \,^{\circ}\text{pF} (50 \,^{\circ}\text{pF for } 7261 \,^{\circ}\text{B} - 23)$

|                                                                          |                    |     |     | Li: | mits  |     |      | _    |                                       |

|--------------------------------------------------------------------------|--------------------|-----|-----|-----|-------|-----|------|------|---------------------------------------|

| Parameter                                                                | _                  |     | 61A |     | 18-18 |     | B-23 | _    | Test                                  |

|                                                                          | Symbol             | Min | Max | Min | Max   | Min | Max  | Unit | Conditions                            |

| Processor Interface                                                      |                    |     |     |     |       |     |      |      |                                       |

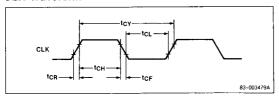

| Clock cycle                                                              | tcy                | 83  |     | 55  |       | 43  |      | ns   |                                       |

| Clock time, low                                                          | t <sub>CL</sub>    | 30  |     | 20  |       | 15  |      | ns   |                                       |

| Clock time, high                                                         | t <sub>CH</sub>    | 30  |     | 20  |       | 17  |      | ns   |                                       |

| Clock rise time                                                          | t <sub>CR</sub>    |     | 10  |     | 10    |     | 10   | ns   |                                       |

| Clock fall time                                                          | t <sub>CF</sub>    |     | 10  |     | 10    |     | 10   | ns   |                                       |

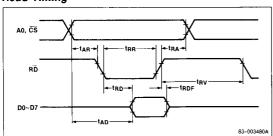

| A <sub>0</sub> , CS setup to RD                                          | t <sub>AR</sub>    | 0   |     | 0   |       | 0   |      | ns   |                                       |

| A <sub>0</sub> , $\overline{\text{CS}}$ hold from $\overline{\text{RD}}$ | t <sub>RA</sub>    | 0   |     | 0   |       | 0   |      | ns   |                                       |

| RD pulse width                                                           | t <sub>RR</sub>    | 200 |     | 100 |       | 100 |      | ns   | · · · · · · · · · · · · · · · · · · · |

| Data delay from RD                                                       | t <sub>RD</sub>    |     | 150 |     | 85    |     | 85   | ns   |                                       |

| Output float delay                                                       | t <sub>RDF</sub>   | 0   | 100 | 0   | 75    | 0   | 75   | ns   |                                       |

| Data delay from A <sub>0</sub> , $\overline{\text{CS}}$                  | t <sub>AD</sub>    |     | 150 |     | 85    |     | 85   | ns   |                                       |

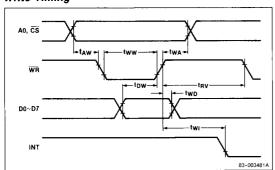

| A <sub>0</sub> , $\overline{\text{CS}}$ setup to $\overline{\text{WR}}$  | t <sub>AW</sub>    | 0   |     | 0   |       | 0   |      | ns   |                                       |

| A <sub>0</sub> , CS hold from WR                                         | t <sub>WA</sub>    | 0   |     | 0   |       | 0   |      | ns   |                                       |

| WR pulse width                                                           | tww                | 200 |     | 100 |       | 100 |      | ns   |                                       |

| Data setup to WR                                                         | t <sub>DW</sub>    | 100 |     | 55  |       | 55  |      | ns   |                                       |

| Data hold from WR                                                        | t <sub>WD</sub>    | 5   |     | 5   | 1 -   | 5   |      | ns   |                                       |

| Recovery time from RD, WR                                                | t <sub>RV</sub>    | 200 |     | 70  |       | 70  |      | ns   |                                       |

| Reset pulse width                                                        | t <sub>RES</sub>   | 100 |     | 100 |       | 100 |      | tcy  |                                       |

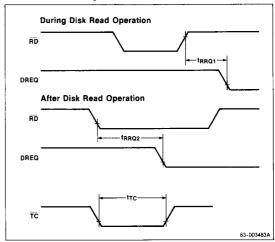

| TC pulse width                                                           | t <sub>TC</sub>    | 100 |     | 100 |       | 80  |      | ns   |                                       |

| INT delay from WR ↑                                                      | t <sub>WI</sub>    |     | 200 |     | 200   |     | 200  | ns   |                                       |

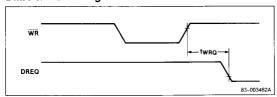

| DREQ delay from WR 1                                                     | twra               |     | 250 |     | 125   |     | 125  | ns   |                                       |

| DREQ delay from RD 1                                                     | t <sub>RRQ1</sub>  |     | 250 |     | 160   |     | 160  | ns   | During disk read operation            |

| DREQ delay from RD ↓                                                     | t <sub>RRQ2</sub>  |     | 150 |     | 130   |     | 100  | ns   | After disk read operation             |

| ST506-Type Interface                                                     |                    |     | •   |     |       |     |      |      |                                       |

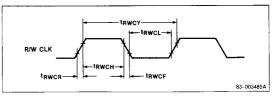

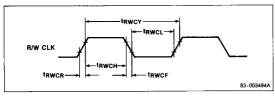

| R/W CLK cycle period                                                     | t <sub>RWCY</sub>  | 83  |     | 83  |       | 83  | ns   |      |                                       |

| R/W CLK time, low                                                        | t <sub>RWCL</sub>  | 30  |     | 30  | ·     | 30  | ns   |      |                                       |

| R/W CLK time, high                                                       | tRWCH              | 30  |     | 30  |       | 30  | ns   |      |                                       |

| R/W CLK rise time                                                        | t <sub>RWCR</sub>  |     | 10  |     | 10    |     | 10   | ns   |                                       |

| R/W CLK fall time                                                        | tRWCF              |     | 10  |     | 10    | . ' | 10   | ns   |                                       |

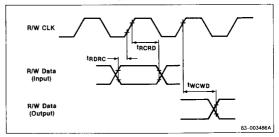

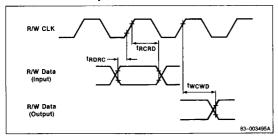

| R/W DATA setup to R/W CLK                                                |                    | 40  |     | 35  |       | 35  |      | ns   |                                       |

| R/W DATA hold from R/W<br>CLK                                            | trcrd              | 5   |     | 5   | •     | 5   |      | ns   |                                       |

| R/W DATA delay from R/W<br>CLK                                           | twcwd              | 35  | 90  | 10  | 60    | 10  | 60   | ns   |                                       |

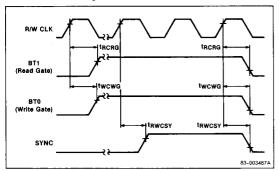

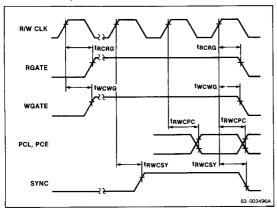

| RGATE delay from R/W CLK                                                 | t <sub>RCRG</sub>  |     | 300 |     | 300   |     | 300  | ns   |                                       |

| WGATE delay from R/W CLK                                                 | twcwg              |     | 150 |     | 150   |     | 150  | ns   |                                       |

| PCE / PCL delay from R/W<br>CLK                                          | t <sub>RWCPC</sub> | 35  | 110 | 10  | 80    | 10  | 80   | ns   |                                       |

| SYNC delay from R/W CLK                                                  | t <sub>RWCSY</sub> |     | 150 |     | 150   |     | 150  | ns   |                                       |

# **AC Characteristics (cont)**

|                                |                    | Limits |     |      |               |      |      | _                 |                                     |  |

|--------------------------------|--------------------|--------|-----|------|---------------|------|------|-------------------|-------------------------------------|--|

|                                | _                  | 72     | B1A | 7261 | <b>18</b> -18 | 7261 | B-23 | _                 | Test                                |  |

| Parameter S                    | Symbol             | Min    | Max | Min  | Max           | Min  | Max  | Unit              | Conditions                          |  |

| ST506-Type Interface (cont)    |                    |        | •   |      |               |      |      |                   |                                     |  |

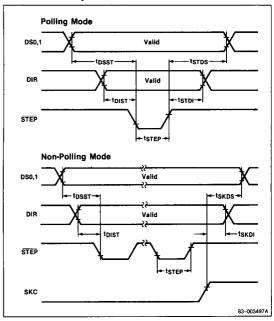

| DS0, DS1 setup to STEP         | t <sub>DSST</sub>  | 250    |     | 250  |               | 250  |      | t <sub>CY</sub>   | Normal seek mode                    |  |

| DIR setup to STEP              | t <sub>DIST</sub>  | 200    |     | 200  |               | 200  |      | t <sub>CY</sub>   |                                     |  |

| STEP pulse width               | tstep              | 69     | 85  | 69   | 85            | 69   | 85   | t <sub>CY</sub>   |                                     |  |

| DS0, DS1 hold from STEP        | t <sub>STDS</sub>  | 750    |     | 750  |               | 750  |      | t <sub>CY</sub>   | Normal seek mode;<br>polling mode   |  |

| DIR hold from STEP             | t <sub>STDI</sub>  | 750    |     | 750  |               | 750  |      | t <sub>CY</sub>   |                                     |  |

| DS0, DS1 hold from SKC         | t <sub>SKDS</sub>  | 100    |     | 100  |               | 100  |      | t <sub>CY</sub>   | Normal seek mode;<br>nonpolling     |  |

| DIR hold from SKC              | t <sub>SKDI</sub>  | 100    |     | 100  |               | 100  |      | t <sub>CY</sub>   |                                     |  |

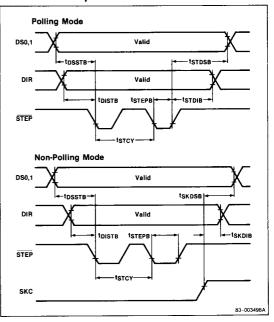

| DS0, DS1 setup to STEP         | †DSSTB             | 250    |     | 250  |               | 250  |      | tcy               | Buffered seek mode                  |  |

| DIR setup to STEP              | tDISTB             | 200    |     | 200  |               | 200  |      | t <sub>CY</sub>   | -                                   |  |

| STEP pulse width               | <sup>†</sup> STEPB | 69     | 85  | 69   | 85            | 69   | 85   | t <sub>CY</sub>   | -                                   |  |

| STEP cycle period              | tstcy              | 500    | 660 | 500  | 660           | 500  | 660  | tcy               |                                     |  |

| DS0, DS1 hold from STEP        | t <sub>STDSB</sub> | 200    |     | 200  |               | 200  |      | t <sub>CY</sub>   | Buffered seek mode;<br>polling mode |  |

| DIR hold from STEP             | †STDIB             | 200    |     | 200  |               | 200  |      | tcy               |                                     |  |

| DS0, DS1 hold from SKC         | tskosb             | 100    |     | 100  |               | 100  |      | t <sub>CY</sub>   | Buffered seek mode;<br>nonpolling   |  |

| DIR hold from SKC              | tskdib             | 100    |     | 100  |               | 100  |      | t <sub>CY</sub>   |                                     |  |

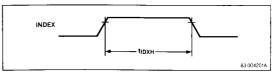

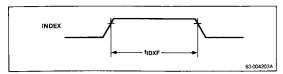

| Index pulse width              | t <sub>IDXF</sub>  | 8      |     | 8    |               | 8    |      | t <sub>RWCY</sub> |                                     |  |

| SMD Interface                  |                    |        |     |      |               |      |      |                   |                                     |  |

| R/W CLK cycle period           | t <sub>RWCY</sub>  | 83     |     | 55   |               | 43   |      | ns                |                                     |  |

| R/W CLK time, low              | tRWCL              | 30     |     | 20   |               | 15   |      | ns                |                                     |  |

| R/W CLK time, high             | tRWCH              | 30     |     | 20   |               | 17   |      | ns                |                                     |  |

| R/W CLK rise time              | tRWCR              |        | 10  |      | 10            |      | 10   | ns                |                                     |  |

| R/W CLK fall time              | tRWCF              |        | 10  |      | 10            |      | 10   | ns                |                                     |  |

| R/W DATA setup to R/W CLK      | t <sub>RDRC</sub>  | 40     |     | 35   |               | 35   | ns   |                   |                                     |  |

| R/W DATA hold from R/W<br>CLK  | t <sub>RCRD</sub>  | 5      |     | 5    |               | 5    |      | ns                |                                     |  |

| R/W DATA delay from R/W<br>CLK | twcwd              | 35     | 90  | 10   | 60            | 10   | 50   | ns                |                                     |  |

| BT1 delay from R/W CLK         | tRCRG              |        | 300 |      | 300           |      | 300  | ns                |                                     |  |

| BT0 delay from R/W CLK         | twcwg              |        | 150 |      | 150           |      | 150  | ns                |                                     |  |

| SYNC delay from R/W CLK        | tRWCSY             |        | 150 |      | 150           |      | 150  | ns                |                                     |  |

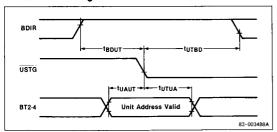

| BDIR setup to USTG             | t <sub>BDUT</sub>  | 60     |     | 60   |               | 60   |      | t <sub>CY</sub>   | Unit select operation               |  |

| BDIR hold from USTG            | t <sub>UTBD</sub>  | 15     |     | 15   |               | 15   |      | t <sub>CY</sub>   | _                                   |  |

| Unit ADR setup to USTG         | tuaut              | 38     | 52  | 38   | 52            | 38   | 52   | tcy               | _                                   |  |

| Unit ADR hold from USTG        | †utua              | 15     |     | 15   |               | 15   |      | t <sub>CY</sub>   |                                     |  |

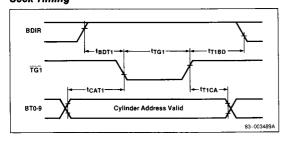

| BDIR setup to TG1              | t <sub>BDT1</sub>  | 27     | 48  | 27   | 48            | 27   | 48   | tcy               | Cylinder select operation           |  |

| BDIR hold from TG1             | t <sub>T1BD</sub>  | 60     |     | 60   |               | 60   |      | t <sub>CY</sub>   | -                                   |  |

# **AC Characteristics (cont)**

|                                 |                    | 72   | 61A | 726 | 1B-18 | 726   | 1B-23 | _               | Test                                                 |

|---------------------------------|--------------------|------|-----|-----|-------|-------|-------|-----------------|------------------------------------------------------|

| Parameter                       | Symbol             | Min  | Max | Min | Max   | Min   | Max   | Unit            | Conditions                                           |

| SMD Interface (cont)            |                    | **** |     |     |       | . 200 |       |                 |                                                      |

| CYL. ADR setup to TG1           | t <sub>CAT1</sub>  | 27   | 48  | 27  | 48    | 27    | 48    | t <sub>CY</sub> | Cylinder select operation                            |

| CYL. ADR hold from TG1          | t <sub>T1CA</sub>  | 24   |     | 24  |       | 24    |       | tcy             | _                                                    |

| TG1 pulse width                 | t <sub>TG1</sub>   | 24   | 36  | 24  | 36    | 24    | 36    | tcy             | _                                                    |

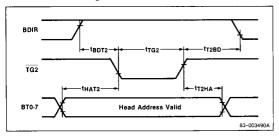

| BDIR setup to TG2               | t <sub>BDT2</sub>  | 15   |     | 15  |       | 15    |       | tcy             | Head select operation                                |

| BDIR hold from TG2              | t <sub>T2BD</sub>  | 70   |     | 70  |       | 70    |       | t <sub>CY</sub> | _                                                    |

| HEAD ADR setup TG2              | t <sub>HAT2</sub>  | 15   | 70  | 15  | 70    | 15    | 70    | tcy             | -                                                    |

| HEAD ADR hold from TG2          | t <sub>T2HA</sub>  | 24   |     | 24  |       | 24    |       | t <sub>CY</sub> | _                                                    |

| TG2, pulse width                | t <sub>TG2</sub>   | 24   | 36  | 24  | 36    | 24    | 36    | t <sub>CY</sub> | -                                                    |

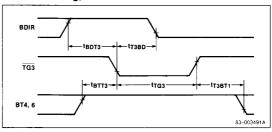

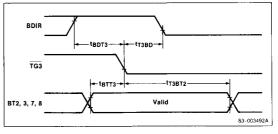

| BDIR setup to TG3               | t <sub>BDT3</sub>  | 24   |     | 24  |       | 24    |       | t <sub>CY</sub> | RT2, FAULT CLR,<br>SERVO, DATA STB<br>control timing |

| BDIR hold from TG3              | t <sub>T3BD</sub>  | 24   | 36  | 24  | 36    | 24    | 36    | t <sub>CY</sub> | _                                                    |

| TG3, pulse width                | t <sub>TG3</sub>   | 56   | 100 | 56  | 100   | 56    | 100   | t <sub>CY</sub> | _                                                    |

| BT2, 3, 4, 6, 7, 8 setup to TG3 | t <sub>BTT3</sub>  |      | 56  |     | 56    |       | 56    | t <sub>CY</sub> | -                                                    |

| BT4, 6 hold from TG3            | t <sub>T3BT1</sub> | 24   |     | 24  |       | 24    |       | t <sub>CY</sub> | _                                                    |

| BT2, 3, 7, 8 hold from TG3      | t <sub>T3BT2</sub> | 75   |     | 75  |       | 75    |       | t <sub>CY</sub> | _                                                    |

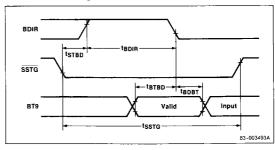

| BDIR delay from SSTG            | †STBD              | 24   |     | 24  |       | 24    |       | t <sub>CY</sub> | Sense unit status timing                             |

| BDIR high time                  | t <sub>BDIR</sub>  | 54   | 66  | 54  | 66    | 54    | 66    | t <sub>CY</sub> | _                                                    |

| BT9 setup to BDIR               | t <sub>BTBD</sub>  | 38   | 52  | 38  | 52    | 38    | 52    | t <sub>CY</sub> | _                                                    |

| BT9 hold from BDIR              | t <sub>BDBT</sub>  | 24   | 33  | 24  | 33    | 24    | 33    | t <sub>CY</sub> | _                                                    |

| SSTG pulse width                | tsstg              |      | 370 |     | 370   |       | 370   | t <sub>CY</sub> |                                                      |

| Index pulse width               | t <sub>IDXH</sub>  | 8    |     | 8   |       | 8     |       |                 |                                                      |

| SCT pulse width                 | t <sub>SCT</sub>   | 8    |     | 8   |       | 8     |       |                 |                                                      |

# Timing Waveforms — Host System Interface

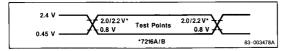

# AC Test Points (Except R/W CLK, CLK)

#### **CLK Waveform**

# Read Timing

# Write Timing

# **DMA Write Timing**

# **DMA Read Timing**

#### Reset Waveform

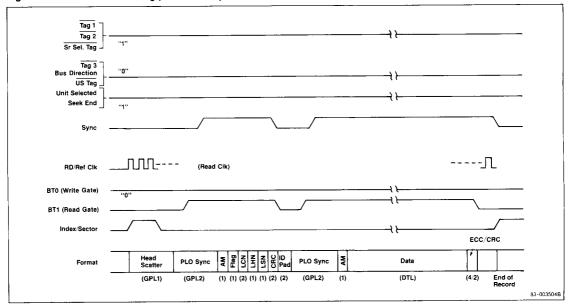

# Timing Waveforms — SMD Interface

# R/W CLK Waveform

# Data Read/Write Timing

# Timing Waveforms — SMD Interface (cont)

## Read/Write Timing

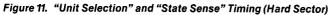

## **Unit Select Timing**

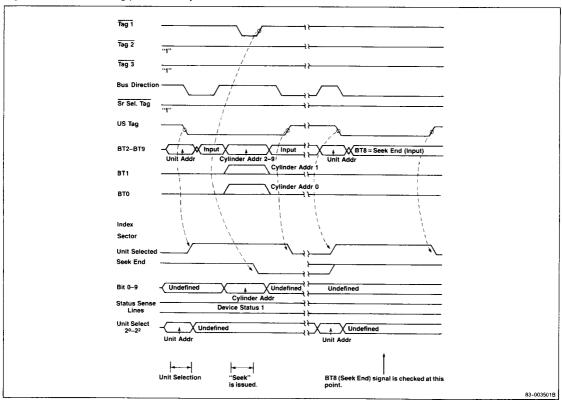

# Seek Timing

## **Head Select Timing**

# Bit Bus Timing, Fault Clear/Return-to-Zero

# Bit Bus Timing, Servo Offset/Data Strobe

## Bit Bus 9 Timing

#### Index Waveform

## Sector Waveform

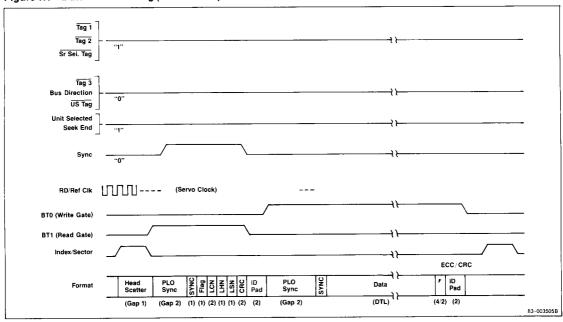

# Timing Waveforms — ST506-Type Interface

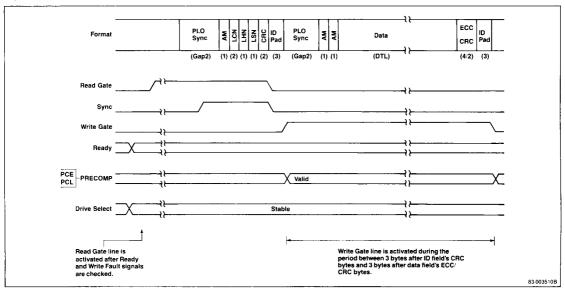

#### Data Read/Write Operation

## Read/Write Operation

## R/W CLK Waveform

#### Index Waveform

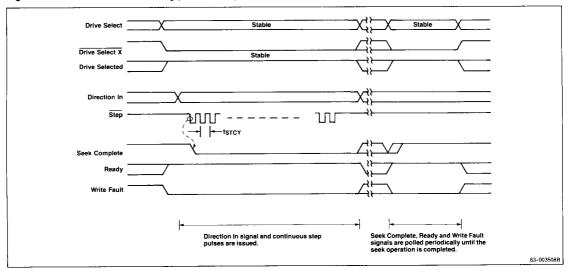

## Normal Seek Operation

## **Buffered Seek Operation**

# Timing Waveforms — ST506-Type Interface (cont)

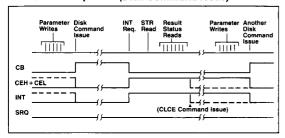

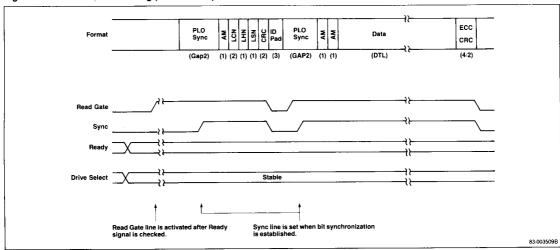

#### Read/Write Sequence (Disk Command Issue)

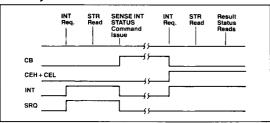

# Sense Interrupt Status Request When Controller Not Busy

## Sense Interrupt Status Request When Controller Busy

#### **High-Level Commands**

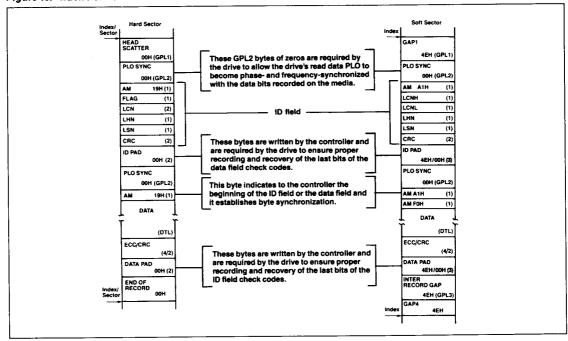

## Specify

Allows user to select SMD or ST506-type mode data block length, ending track number, end sector number, gap length, track at which write current is reduced, ECC or CRC function, choice of polynomial, and polling mode enable.

## **Sense Interrupt Status**

When a change of disk status occurs, the HDC will interrupt the host CPU. This command will reveal the cause of interrupt, such as seek end, disk ready change, seek error, or equipment check. The disk unit address is also supplied.

#### **Sense Unit Status**

The host CPU specifies the drive numbers and the HDC will return information such as write fault, ready, track 000, seek complete and drive selected, or for SMD units fault, seek error, on cylinder, unit ready, AM found, write protected, seek end, and unit selected.

#### **Detect Error**

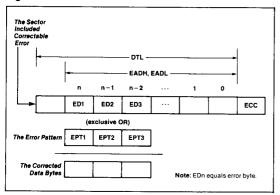

Used after a read operation where ECC has been employed. The detect error command supplies the information needed to allow the host CPU to execute an error correction routine. (Only allowed when an actual correctable error is detected by the HDC.)

#### Recalibrate

Returns the disk drive heads to the home position or track 000 position. Has four modes of operation: SMD, normal, buffered, or nonpolling.

#### Seek

Moves the disk drive heads to the specified cylinder. As in recalibrate, seek has four modes of operation.

#### **Format**

This command is used to initialize the medium with the desired format which includes various gap lengths, data patterns, and CRC codes. This command is used in conjunction with the specify command.

## Verify ID

Used to verify the ID bytes with data from memory. Performs the operation over a specified number of sectors.

#### Read ID

Used to verify the position of the read/write heads.

## Read Diagnostic

Used in SMD mode only, the command allows the programmer to read a sector of data even if the ID portion of the sector is defective. Only one sector at a time can be read.

#### **Read Data**

Reads and transfers to the system memory the number of sectors specified. The HDC can read multiple sectors and multiple tracks with one instruction.

#### Scan

Compares a specified block of memory with specified sectors on the disk. The 7261A/7261B continues until a sector with matching data is found, until the sector count reaches zero, or the end of the cylinder is reached.

#### **Verify Data**

Makes a sector-by-sector comparison of data in the system memory by DMA transfer. As in read operation, multiple sectors and tracks may be verified with this command.

#### **Write Data**

Data from the system memory, transferred by DMA, is written onto the specified disk unit. As in the read command, data may be written onto successive sectors and tracks.

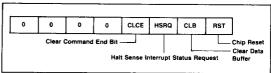

## **Auxiliary Command**

Allows four additional functions to be executed: software reset, clear data buffer, mask interrupt request bit (masks interrupts caused by change of status of drives), and reset interrupt caused by command termination (used when no further disk commands will be issued, which would normally reset the interrupt).

## **Command Operation**

There are three phases for most of the instructions that the  $\mu PD7261A/7261B$  can execute: command phase, execution phase, and result phase. During the command phase the host CPU loads preset parameters into the  $\mu PD7261A/7261B$  FIFO via the data bus and by successive write pulses to the part with  $A_0$  and CS true low. Once the required parameter bytes are loaded the appropriate command is initiated by issuing a write pulse with  $A_0$  high and CS low and the command code on the data bus.

The μPD7261A/7261B is now in the execution phase. This can be verified by examining the status register bit 7 (the controller busy bit). The execution phase is ended when a normal termination or an abnormal termination occurs. An abnormal termination can occur due to a read or write error, or a change of status in the addressed disk drive. A normal termination occurs when the command given is correctly completed. (This is indicated by bits in the status register.) The result phase is then entered. The host CPU may read various result parameters from the FIFO. These result parameters may be useful in determining the cause of an interrupt, or the location of a sector causing a read error, for example.

The chart shown in table 2 illustrates the preset parameters and result parameters that are associated with each command. The abbreviations are defined at the end of table 2.

Table 2. Preset Parameters and Result Status Byte

| Disk                      | Command |      |        |        |      |             |        |                   |        |  |

|---------------------------|---------|------|--------|--------|------|-------------|--------|-------------------|--------|--|

| Command                   | Code    | 1st  | 2nd    | 3rd    | 4th  | 5th         | 6th    | 7th               | 8th    |  |

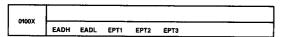

| Detect error              | 0100X   |      |        |        |      |             |        |                   |        |  |

|                           |         | EADH | EADL   | EPT1   | EPT2 | EPT3        |        |                   |        |  |

| Recalibrate               | 0101[B] |      |        |        |      |             |        |                   |        |  |

|                           |         | IST* |        |        |      |             |        |                   |        |  |

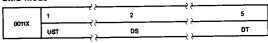

| Seek                      | 0110[B] | PCNH | PCNL   |        |      |             |        |                   |        |  |

|                           |         | IST* |        |        |      |             |        |                   |        |  |

| Format                    | 0111(S) | PHN  | (PSN)  | SCNT   | DPAT | GPL1        | [GPL3] |                   |        |  |

|                           |         | EST  | SCNT   |        |      |             |        |                   |        |  |

| Verify ID                 | 1000(S) | PHN  | (PSN)  | SCNT   |      |             |        |                   |        |  |

|                           |         | EST  | SCNT   |        |      |             |        |                   |        |  |

| Read ID                   | 1001(S) | PHN  | (PSN)  | SCNT   |      |             |        |                   |        |  |

|                           |         | EST  | SCNT   |        |      |             |        |                   |        |  |

| (Read diagnostic)         | 1010X   | PHN  | PSN    |        |      |             |        |                   |        |  |

|                           |         | EST  |        |        |      |             |        |                   |        |  |

| Read data                 | 1011X   | PHN  | (FLAG) | LCNH   | LCNL | LHN         | LSN    | SCNT              |        |  |

|                           |         | EST  | PHN    | (FLAG) | LCNH | LCNL        | LHN    | LSN               | SCNT   |  |

| Check                     | 1100X   | PHN  | (FLAG) | LCNH   | LCNL | LHN         | LSN    | SCNT              | _      |  |

|                           |         | EST  | PHN    | (FLAG) | LCNH | LCNL        | LHN    | LSN               | SCNT   |  |

| Scan                      | 1101X   | PHN  | (FLAG) | LCNH   | LCNL | LHN         | LSN    | SCNT              | **     |  |

|                           |         | EST  | PHN    | (FLAG) | LCNH | LCNL        | LHN    | LSN               | SCNT   |  |

| Verify data               | 1110X   | PHN  | (FLAG) | LCNH   | LCNL | LHN         | LSN    | SCNT              |        |  |

|                           |         | EST  | PHN    | (FLAG) | LCNH | LCNL        | LHN    | LSN               | SCNT   |  |

| Write data                | 1111X   | PHN  | (FLAG) | LCNH   | LCNL | LHN         | LSN    | SCNT              |        |  |

|                           |         | EST  | PHN    | (FLAG) | LCNH | LCNL        | LHN    | LSN               | SCNT   |  |

| Sense interrupt<br>status | 0001X   | IST  |        |        |      | ·· <u> </u> |        |                   | -      |  |

| Specify                   | 0010X   | MODE | DTLH   | DTLL   | ETN  | ESN         | GPL2   | (MGPL1)<br>[RWCH] | [RWCL] |  |

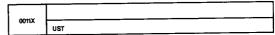

| Sense unit status         | 0011X   |      |        |        |      |             |        |                   |        |  |

|                           |         | UST  |        |        |      |             |        |                   |        |  |

### Note:

- (): These are omitted for soft-sector disks.

- []: These are omitted for hard-sector disks.

- \*: IST available as a result byte only when in nonpolling mode.

- B: Indicates buffered mode when set.

- S: Indicates Skewed mode (SMD only) when set.

- X: Indicates don't care.

#### **Mnemonic Definitions**

EADH Error address, high byte

EADL Error address, low byte

EPT1 Error pattern, byte one

EPT2 Error pattern, byte two

EPT3 Error pattern, byte three

PCNH Physical cylinder number, high byte

# Mnemonic Definitions (cont)

PCNL Physical cylinder number, low byte

PHN Physical head number

PSN Physical sector number

SCNT Sector count

DPAT Data pattern

GPL1 Gap length one

GPL3 Gap length three

EST Error status byte

FLAG Flag byte

LCNH Logical cylinder number, high byte

| LCNL  | Logical cylinder number, low byte |

|-------|-----------------------------------|

| LHN   | Logical head number               |

| LSN   | Logical sector number             |

| IST   | Interrupt status byte             |

| MODE  | Mode                              |

| DTLH  | Data length, high byte            |

| DTLL  | Data length, low byte             |

| ETN   | Ending track number               |

| ESN   | Ending sector number              |

| GPL2  | Gap length two                    |

| RWCL  | Write current cylinder, low byte  |

| RWCH  | Write current cylinder, high byte |

| UST   | Unit status byte                  |

| MGPL1 | Modified gap length 1             |

# **Status Register**

This register is a read only register and may be read by asserting  $\overline{RD}$  and  $\overline{CS}$  with  $A_0$  high. The status register may be read at any time. It is used to determine controller status and partial result status. See table 3.

Table 3. Status Register Bits

|                                 | Pin                       |                                                                                                                                                                                                                                                                       |

|---------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.                             | Name                      | Function                                                                                                                                                                                                                                                              |

| D <sub>7</sub>                  | CB<br>(Controller busy)   | Set by a disk command issue. Cleared when the command is completed. (This bit is also set by an external reset signal or an RST command, but will be cleared at the completion of the reset function.) When this bit is set, a new disk command will not be accepted. |

| D <sub>6</sub> , D <sub>5</sub> | CEH, CEL<br>(Command end) | CEH = 0 and CEL = 0  A disk command is in process, or no disk command is issued after the last reset signal or the last CLCE auxiliary command. Both the CEH and CEL bits are cleared by a disk command, a CLCE auxiliary command, or a rese signal.                  |

|                                 |                           | CEH = 0 and CEL = 1 Abnormal termination of a disk command. Execution of a disk command was started, but was not successfully completed.                                                                                                                              |

|                                 |                           | CEH = 1 and CEL = 0  Normal termination of a disk command. The execution of a disk command was completed and properly executed.                                                                                                                                       |

|                                 |                           | CEH = 1 and CEL = 1 Invalid command issue.                                                                                                                                                                                                                            |

Table 3. Status Register Bits (cont)

|                | Pin                                        |                                                                                                                                                                                                                                                                                                                                      |

|----------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.            | Name                                       | Function                                                                                                                                                                                                                                                                                                                             |

| D <sub>4</sub> | SRQ<br>(Sense interrupt<br>status request) | When a seek end, an equipmen check condition, or a ready signa state change is detected, this bit is se requesting a sense interrupt status command be issued to take the de tailed information. This bit is cleared by an issue of that command or by reset signal.                                                                 |

| D <sub>3</sub> | RRQ<br>(Reset request)                     | Set when controller has lost control of<br>the format controller (missing addres<br>mark, for example). An auxiliary RS<br>command or RESET signal will cleat<br>this bit.                                                                                                                                                           |

| D <sub>2</sub> | IER<br>(ID error)                          | Set when a CRC error is detected in the ID field. An auxiliary RST or an other disk command will reset this bit                                                                                                                                                                                                                      |

| D <sub>1</sub> | NCI<br>(Not coincident)                    | Set if the controller cannot find a sector on the cylinder which meets the comparison condition during the execution of a scan command. This bit is also set if data from the disk does no coincide with the data from the system during a verify ID or a verify dat command. This bit is cleared by a discommand or a reset signal. |

| D <sub>0</sub> | DRQ<br>(Data request)                      | During execution of write ID, verify ID scan, verify data, or a write data command, this bit is set to request the data be written into the data buffe During execution of read ID, read of agnostic, or read data command, the bit is set to request that data be reaftrom the data buffer.                                         |

#### **Error Status Byte**

This byte is available to the host at the termination of a read, write, or data verification command and provides additional error information to the host CPU. If the status register indicates a normal command termination, it can be assumed that the command was executed without error and it is not necessary to read this byte. When it is necessary to determine the cause of an error this byte may be read by issuing an  $\overline{\text{RD}}$  pulse with  $\overline{\text{CS}}$  and  $A_0$  low. The remaining result bytes associated with a particular command may be read by issuing additional  $\overline{\text{RD}}$  pulses. Data transfer from or to the FIFO is asynchronous and may occur at rates up to 2.5 Mbytes per second. See table 4.

Table 4. Error Status Bits

|                | Pin                           |                                                                                                                                                                                                                                             |

|----------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.            | Name                          | Function                                                                                                                                                                                                                                    |

| D <sub>7</sub> | ENC<br>(End of cylinder)      | Set when the controller tries to access a sector beyond the final sector of a cylinder. Cleared by a disk command or an auxiliary RST command.                                                                                              |

| D <sub>6</sub> | OVR<br>(Overrun)              | When set, indicates that the FIFO became full during a read operation, or empty during a write operation.                                                                                                                                   |

| D <sub>5</sub> | DER<br>(Data error)           | A CRC or an ECC error was detected in the data field.                                                                                                                                                                                       |

| D <sub>4</sub> | EQC<br>(Equipment check)      | A fault signal from the drive has been detected or a track 0 signal has not been returned within a certain time interval after the recalibrate command was issued.                                                                          |

| $D_3$          | NR<br>(Not ready)             | The drive is not in ready state.                                                                                                                                                                                                            |

| D <sub>2</sub> | ND<br>(No data)               | The sector specified by ID parameters was not found on the track.                                                                                                                                                                           |

| D <sub>1</sub> | NWR<br>(Not writable)         | Set if write protect signal is detected when the controller tries to write on the disk. It is cleared by a disk command or by an auxiliary RST command.                                                                                     |

| D <sub>0</sub> | MAM<br>(Missing address mark) | This bit is set if during execution of read data, check, scan, or verify data commands, no address mark was found in the data field or if during execution of a read ID or verify ID command, no address mark was detected in the ID field. |

### **Interrupt Status Byte**

This byte is made available to the host CPU by executing the Sense Interrupt Status command. This command should be issued only when the  $\mu$ PD7261A/7261B requests it, as indicated by bit D<sub>4</sub> of the status register. This byte reveals changes in disk drive status that have occurred. See table 5.

Table 5. Interrupt Status Bits

|                                | Pin                                                |                                                                                                                |  |  |  |  |

|--------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| No.                            | Name                                               | Function                                                                                                       |  |  |  |  |

| D <sub>7</sub>                 | SEN<br>(Seek end)                                  | A seek end or seek complete signal<br>has been returned after a seek or a re-<br>calibrate command was issued. |  |  |  |  |

| D <sub>6</sub>                 | RC<br>(Ready change)                               | The state of the ready signal from the<br>drives has changed. The state itself is<br>indicated by the NR bit.  |  |  |  |  |

| D <sub>5</sub>                 | SER<br>(Seek error)                                | Seek error has been detected on seek end.                                                                      |  |  |  |  |

| D <sub>4</sub>                 | EQC<br>(Equipment check)                           | Identical to bit 4 of the error status byte.                                                                   |  |  |  |  |

| D <sub>3</sub>                 | NR<br>(Not ready)                                  | Identical to bit 3 of the error status byte.                                                                   |  |  |  |  |

| D <sub>2</sub> -D <sub>0</sub> | UA <sub>2</sub> -UA <sub>0</sub><br>(Unit address) | The unit address of the drive which caused an interrupt request on any of the above conditions.                |  |  |  |  |

#### **Drive Interface**

The µPD7261A/7261B has been designed to implement two of the more popular types of interfaces: the SMD (Storage Module Drive) and the floppy-like Winchester drive which has come to be known as the ST506 interface. The desired interface mode is selected by the Specify command.

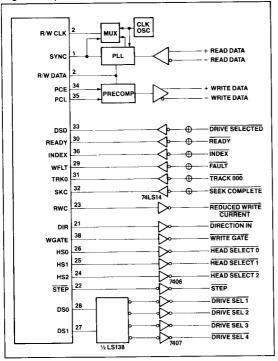

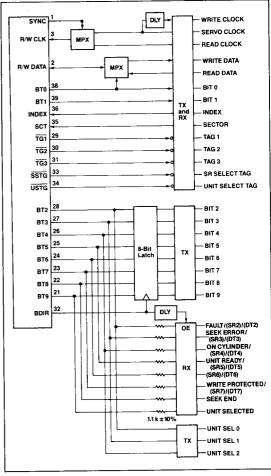

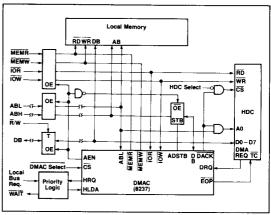

# ST506-Type Interface

In the ST506 mode the  $\mu$ PD7261A/7261B performs MFM encoding and decoding at data rates to 6 MHz and provides all necessary drive interface signals. Included internally is circuitry for address mark detection, sync area recognition, serial-to-parallel-to-serial conversion, an 8-byte FIFO for data buffering, and circuitry for logical addressing of the drives. External circuitry required consists of control signal buffering, a delay network for precompensation, a phase-lock loop, a write clock of cillator and a differential transceiver for drive data. The floppy-like interface can be implemented with as few as 7 IC's using NEC's hard-disk interface chip, the  $\mu$ PD9306A, or with 12 to 14 SSI ICs. See figure 1.

NEC

### **SMD** Interface

In the SMD mode the  $\mu$ PD7261A/7261B will support data rates to 10 MHz/15 MHz in the NRZ format. All control functions necessary for an SMD interface are implemented on-chip with de-multiplexing of 8 data lines performed externally by a single 8-bit latch. A small amount of logic is required to multiplex the data and clock lines, and differential drivers and receivers are required to implement the actual interface. Depending on individual logic design and the number of drives used, the SMD interface may be implemented with as few as 12 ICs. See figure 2.

#### Note:

CLK (pin 37) frequency must be a minimum of 1.1 imes NRZ data rate.

#### **Internal Architecture**

The  $\mu$ PD7261A/7261B can be divided into three major internal logic blocks: command processor; format controller; microprocessor interface.

#### **Command Processor**

The command processor is an 8-bit microprocessor with its own instruction set, program ROM, scratchpad RAM, ALU, and I/O interface. Its major functions are:

Figure 2. µPD7261A/7261B SMD Interface

- ☐ To decode the commands from the host microcomputer that are received through the 8-bit data bus

- ☐ To execute seek and recalibrate commands

- ☐ To interface to the drives and read the drive status lines

- To load the format controller with the appropriate microcode, enabling it to execute the various read/ write data commands.

The command processor microprocessor is idle until it receives the command from the host microcomputer. It then reads the parameter bytes from the FIFO, and loads them into its RAM. The command byte is decoded and, depending on its opcode, the appropriate subroutine from the 2.6K internal ROM is selected and executed. Some of these commands are executed by the command processor without involvement of the format

controller. When data transfers to and from the disk are made, the command processor loads the appropriate microcode into the format controller, then relinquishes control. When the data transfer is complete, the command processor again takes control. One other important function that the command processor performs is managing the interface to the disk drives. The command processor contains an I/O port structure similar to many single-chip microcomputers in that the ports may be configured as input or output pins. Depending on the mode of operation selected by the Specify command, the command processor will use the bidirectional I/O lines for different functions.

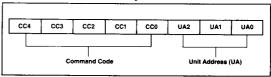

## **Command Register**

This register is a write only register. It is selected when the A<sub>0</sub> input is high and the  $\overline{CS}$  input is low. There are two kinds of commands: disk commands and auxiliary commands. Each command format is shown in figure 3.

An auxiliary command is accepted at any time and is immediately executed, while a disk command is ignored if the on-chip processor is busy processing another disk command. A valid disk command causes the processor to begin execution using the parameters previously loaded into the data buffer. Disk commands and the parameters needed are described in the Microprocessor Interface section.

#### **Command Codes**

|   |   | CC4-CC | ) |      |                            |  |

|---|---|--------|---|------|----------------------------|--|

| 0 | 0 | 0      | 0 | Х    | (Auxiliary Command)        |  |

| 0 | 0 | 0      | 1 | Х    | Sense int. status (Note 1) |  |

| 0 | 0 | 1      | 0 | Х    | Specify (Note 1)           |  |

| 0 | 0 | 1      | 1 | Χ    | Sense unit status          |  |

| 0 | 1 | 0      | 0 | Χ    | Detect error (Note 1)      |  |

| 0 | 1 | 0      | 1 | [B]  | Recalibrate                |  |

| 0 | 1 | 1      | 0 | [B]  | Seek                       |  |

| 0 | 1 | 1      | 1 | [S]  | Format                     |  |

| 1 | 0 | 0      | 0 | [S]  | Verify ID                  |  |

| 1 | 0 | 0      | 1 | [\$] | Read ID                    |  |

| 1 | 0 | 1      | 0 | X    | Read diagnostic            |  |

| 1 | 0 | 1      | 1 | - X  | Read data                  |  |

| 1 | 1 | 0      | 0 | Х    | Check                      |  |

| 1 | 1 | 0      | 1 | Х    | Scan                       |  |

| 1 | 1 | 1      | 0 | Х    | Verify data                |  |

| 1 | 1 | 1      | 1 | Χ    | Write data                 |  |

#### Note:

- (1) The UA field is 000

- [B] Indicates buffered mode when set.

- [S] Indicates skewed mode when set.

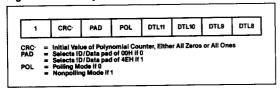

Figure 3. Disk Command Byte

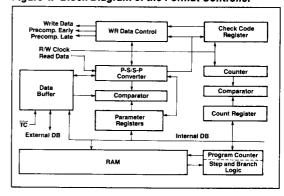

#### **Format Controller**

The format controller is built with logic that enables it to execute instructions at very high speed: one instruction per single clock cycle. The major functions it performs are:

- Serial-to-parallel and parallel-to-serial data conversion

- ☐ CRC and ECC generation and checking

- ☐ MFM data decoding and encoding

- □ Write precompensation

- □ Address mark detection and generation

- □ ID field search in soft-sector format

- DMA data transfer control during read/write operations.

The major blocks in the format controller are the sequencer and the serial/parallel data handler. The sequencer consists of a writable control store (32 words by 16 bits), a program counter, branch logic, and the parameter register. The serial/parallel logic consists of a parallel-to-serial converter for disk write operations, a serial-to-parallel converter for disk read operations, precompensation logic for writing MFM data, comparator logic that locates sync fields, address marks, and ID fields. There is also comparator logic that is used during Verify Data commands. See figure 4.

Figure 4. Block Diagram of the Format Controller

# **Microprocessor Interface**

Read/Write Control. The internal registers are selected as shown in truth table 6.

Table 6. Register Selection Table

| CS A <sub>0</sub> |   | RD | WR | Selection                       |  |  |  |  |

|-------------------|---|----|----|---------------------------------|--|--|--|--|

| 0                 | 0 | 0  | 1  | 1 Data buffer register (Note    |  |  |  |  |

| 0                 | 0 | 1  | 0  | 0 Data buffer register (Note 1) |  |  |  |  |

| 0                 | 1 | 0  | 1  | 1 Status register               |  |  |  |  |

| 0                 | 1 | 1  | 0  | Command register                |  |  |  |  |

| 0 -               | Х | 1  | 1  | Don't care                      |  |  |  |  |

| 1                 | Х | X  | Χ  | Don't care                      |  |  |  |  |

| 0                 | Х | 0  | 0  | Inhibited                       |  |  |  |  |

#### Note:

(1) Preset parameters and result status information are written and read from the result status register in the HDC through this data buffer register.

**Interrupt.** The interrupt request line is activated or inactivated according to the following equation:

This means that if either of the command end bits is set or if the sense interrupt status request bit is set (and the SRQM mask is not set), then an interrupt will be generated. The command end bits, CEH and CEL, are set by command termination.

The SRQ bit is set when an equipment check condition or a state change of the ready signal from the disk drives is detected. It is also set when a seek operation is completed. Under these conditions the INT line is activated unless the SRQM mask is set.

Both of the CEH and CEL bits are cleared by a disk command, but both bits may be cleared before the next disk command by issuing a CLCE auxiliary command.

The interrupt caused by the SRQ bit indicates that a sense interrupt status command should be issued by the host microprocessor so that it can determine the exact cause of the interrupt. However, the  $\mu$ PD7261A/7261B may be processing a disk command when the interrupt occurs. Since it is not possible to issue a disk command while the  $\mu$ PD7261A/7261B is busy, an HSRQ auxiliary command can be issued to set the SRQM (sense interrupt request mask) and mask the interrupt. The SRQM is reset upon completion of the disk command in progress.

**DMA Control.** When true, the DREQ pin and the DRQ (data request) bit of the status register indicate a request for data transfer between the disk controller and external memory. These are activated during execution of the following disk commands:

HDC ← memory: Format, Verify ID, Scan, Verify Data, Write Data

HDC → memory: Read ID, Read Diagnostic, Read Data

Data being read from a disk or external memory is temporarily stored in the data buffer (8 bytes maximum), and is transferred to external memory or a disk, respectively.

Data transfers are terminated externally by a reset signal or by a read or a write data operation coinciding with an active terminal count (TC) signal. They are also terminated internally when an abnormal condition is detected or all the data specified by the sector count parameter (SCNT) has been transferred.

Data transfers are accomplished by  $\overline{\text{RD}}$  or  $\overline{\text{WR}}$  signals to the  $\mu\text{PD7261A/7261B}$  when DREQ is active. During read operations, DREQ goes active when the FIFO contains three or more bytes. If the FIFO contains three bytes and an  $\overline{\text{RD}}$  pulse is issued, DREQ goes low within transparent transparent in the final byte is extracted. In this case, DREQ goes low within transparent transpar

#### Commands

#### Recalibrate

| I | 0101B | IST* |  |

|---|-------|------|--|

The read/write heads of the specified drive are retracted to the cylinder 0 position. IST is available as a result byte only if polling mode is disabled. See Specify.

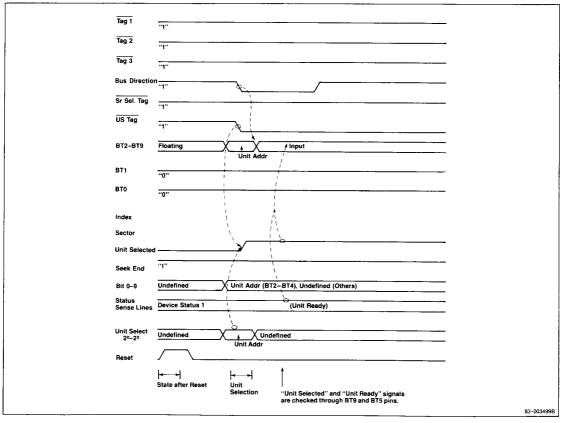

Hard-Sector. An RTZ (Return to Zero) signal is asserted on the bit-6 line with the TAG-3 bit being set. Then the CEH bit of the status register is set indicating a normal termination of the command.

After this command is given, the HDC checks the seek end, unit ready, and fault lines of the drive continually until an active signal is detected on these lines. Then the SRQ bit of the status register is set indicating that a sense interrupt status command should be performed. Each bit of the IST (interrupt status) byte is set according to the result, in anticipation of the sense interrupt status command.

**Soft-Sector.** There are four different ways to implement the Recalibrate command when the ST506 interface mode has been specified. Both polling and nonpolling modes of operation are provided, with both normal or buffered Recalibrate commands available in either mode.

Normal Mode with Polling. The CEH bit of EST is set to 1 immediately after the Recalibrate command is issued (a Recalibrate command may now be issued to another drive). The HDC now begins generating step pulses at the specified rate. The PCN for the drive is cleared and the TRK0 signal is checked while stepping pulses are sent to one or more drives. When TRK0 is asserted, the SEN (seek end) bit of the IST (interrupt status) byte is set and the SRQ bit of the status register is set. This causes an interrupt and requests that a sense interrupt status command be issued. If 1023 pulses have been sent and TRK0 is not asserted, then the SRQ bit is again set, but with the SER (seek error) and EQC (equipment check) bits of the IST byte set. The ready signal of each drive is checked before each step pulse is sent, and the Recalibrate command is terminated if the drive enters a notready state, whereby the NR bit of the IST byte is set to 1.

Normal Mode with Polling Disabled. Operation is similar to that in "Normal Mode with Polling", but the CEH and CEL bits of the status register are not set until either the SEN (seek end) or the SER (seek error) condition occurs. The SRQ bit is not set when polling is disabled, and the IST byte is now available as a result byte when the Recalibrate command is terminated (see "Preset Parameters and Result Status Bytes"). It is not possible to overlap Recalibrate operations in this mode.

**Buffered Mode with Polling.** This mode operates in a manner similar to that described as "Normal Mode with Polling", but with the following differences:

- 1023 step pulses are sent at a high rate of speed (approximately 50 µs between pulses)

- (2) After the required number of pulses are sent, the CEH bit is set, and then additional Recalibrate or Seek commands will be accepted for other drives

- (3) The SRQ bit is set when the drive asserts SKC, which causes the SEN bit of the IST byte to be set

- (4) If SEN is not set within the time it takes to send 1023 "normal" pulses (i.e., when in normal stepping mode), then SER and EQC of the IST byte are set.

**Buffered Mode with Polling Disabled.** 1023 stepping pulses are immediately sent after the Recalibrate command is issued. CEH and/or CEL is set when SEN or SER occurs. SEN is set when TRK0 from the addressed drive is asserted. SER is set if TRK0 is not asserted within the time required to send 1023 "normal" pulses. The Recalibrate command will be terminated abnormally if a not-ready condition occurs prior to SEN being

set. The SRQ bit of the status register is not set. The IST byte (interrupt status) is available as a result byte when either CEH or CEL is set.

#### Seek

| 0110B | PCNH | PCNL |  |

|-------|------|------|--|

| 01108 | IST* |      |  |

PCNH = Physical Cylinder Number, High Byte PCNL = Physical Cylinder Number, Low Byte

The read/write heads of the specified drive are moved to the cylinder specified by PCNH and PCNL. IST is available as a result byte only if polling mode is disabled. See Specify.

Hard-Sector. The contents of PCNH and PCNL are asserted on the BIT0 through BIT9 output lines of the SMD interface with the TAG1 control line being set. (The most significant six bits of PCNH are not used.) The CEH bit of the status register is then set, and the command is terminated normally.

The HDC then checks the seek end, unit ready and fault lines of the drive continually until an active signal is detected on these lines. The SRQ bit of the status register is then set requesting that a Sense Interrupt Status command be performed. Each bit of the IST (interrupt status) byte is set appropriately in anticipation of the Sense Interrupt Status command.

Soft-Sector (Normal Stepping, Polling Enabled). In this mode, the CEH bit of the status register is set to 1 as soon as the Seek command is issued. This allows a Seek or Recalibrate command to be issued to another drive. The HDC now sends stepping pulses at the specified rate and monitors the ready signal. Should the drive enter a not-ready state, the SER bit of the IST byte is set and the SRQ bit of the status register is set, causing an interrupt and requesting a Sense Interrupt Status command. When the drive asserts the seek complete (SKC) signal, the SEN bit of the IST byte is set and the SRQ bit of the status register is set, again requesting service.

Soft-Sector (Normal Stepping, Polling Disabled). Stepping pulses to the drive begin as soon as the Seek command is accepted. The ready signal is checked prior to each step pulse. If the drive enters a not-ready state the seek command is terminated abnormally (CEL = 1), and SER of the IST byte is set. If the seek operation is successful, the seek command will be terminated normally (CEH = 1) when the drive asserts SKC (seek complete). The SEN (seek end) bit of the IST byte is set and the IST (interrupt status) byte is available as a result byte. The Sense Interrupt Status command is not allowed (SRQ is not set), nor can seek operations be overlapped in this mode.

Soft-Sector (Buffered Stepping, Polling Enabled). As soon as the Seek command is accepted by the HDC, high-speed stepping pulses are generated. As soon as the required number of pulses are sent, CEH is set to 1, indicating a normal termination. Another Seek command in the same mode may now be issued. The drive is now controlling its own head positioner and asserts SKC when the target cyclinder is reached.) If the drive has not asserted SKC (seek complete) within the time it takes to send the required number of pulses in normal stepping mode, or if the drive enters a not-ready state, then the SER bit of the IST byte and the SRQ bit of the status register are set. Otherwise, the SEN bit of the IST byte is set, along with SRQ of the status register.

Soft-Sector (Buffered Stepping, Polling Disabled). In this mode, the appropriate number of high-speed stepping pulses are sent as soon as the Seek command is issued. If the drive enters a not-ready state, or if SKC (seek complete) is not asserted within the time it takes to send the required number of pulses in normal stepping mode, then the Seek command is terminated normally (generating an interrupt). The IST byte is available as a result byte and the appropriate bit is set; i.e., SER and EQC or NR (not ready). If the seek operation is successful, the Seek command is terminated normally (CEH = 1) and the SEN bit of the IST byte is set. The IST byte is available as a result byte. The Sense Interrupt Status command is not allowed (SRQ is not set), nor can seek operations be overlapped in this mode.

#### **Format**

| [ |       | PHN | (PSN) | SCNT | DPAT | GPL1 | (GPL3) |  |

|---|-------|-----|-------|------|------|------|--------|--|

| ١ | 0111S | EST | SCNT  |      |      |      |        |  |